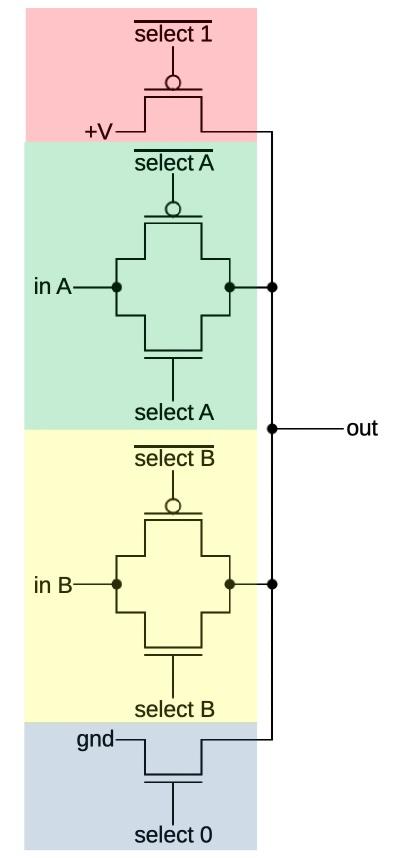

Intel 386 处理器作为 1985 年推出的 x86 架构 32 位芯片,内部集成了 28.5 万个晶体管,其设计复杂度远超前代。为了赶上进度,Intel 首次大规模采用标准单元(standard cell)逻辑设计。这种方法将基本逻辑门(如反相器、与非门)预先设计成固定高度的标准单元,由软件自动放置布线(place and route),极大提升了布局效率。但在 1.5μm CMOS 工艺下,标准单元库中出现了一些非寻常电路设计,特别是通透晶体管(pass-transistor)逻辑,用于构建巨型多路复用器(mux),以处理寄存器选择等复杂控制逻辑。

通透晶体管逻辑的核心优势与实现

通透晶体管逻辑本质上是使用 CMOS 开关(NMOS + PMOS 并联)作为传输门,直接将输入信号 “通透” 到输出,而非传统与 / 或门组合。这种设计在 386 的寄存器控制单元中尤为突出。寄存器选择需处理 30 个寄存器(含 32/16/8 位分割)、方向位翻转、微码指定等约 17 种情况,每路控制信号 7 位宽,总计三路(源 1、源 2、目的),复杂度极高。

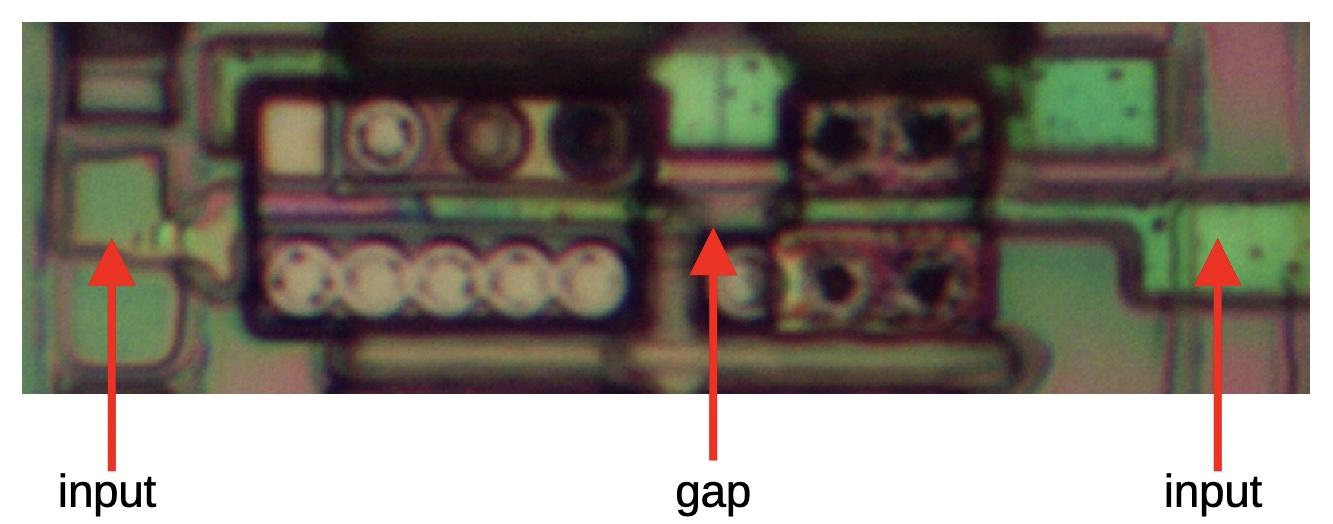

传统静态 CMOS 与 / 或树 mux 会消耗大量面积和功耗,而通透晶体管 mux 只需串联多个传输门,并用反相器恢复信号强度。例如,一个 4 选 1 mux 可由 4 个传输门组成:每个门由互补 NMOS(拉低强)和 PMOS(拉高,但需双倍尺寸补偿弱势)构成,控制线一对(正 / 反相)。在 386 芯片显微镜下,这些单元呈行排列,暗条为晶体管区,轻色间隙为布线通道(routing channel)。

关键参数:

- 传输门尺寸:PMOS 宽度约 NMOS 2-3 倍(1.5μm 工艺 PMOS 迁移率低),确保上升 / 下降时延均衡。

- 信号恢复:每级 mux 后插入反相器对(inverter pair),阈值电压恢复至 Vdd/2,避免累积衰减。时延开销 ≈ 10-20% 比静态门,但面积节省 30-50%。

- 监控点:布线层(M1 垂直内部,M2 水平跨单元),via 密度 < 50% 以防拥塞。

这种设计体现了面积 - 延迟权衡:在面积紧张的 std cell 列中,通透逻辑密度高(单 mux 节省 10+ 静态门),但引入信号弱化风险,需严格控制级数 ≤4-6 级。

非寻常变体:“假反相器” 与错位晶体管

标准单元库中,反相器是最常见单元(百余个,多尺寸优化性能)。但逆向发现 9 个 “假反相器”:硅布局与真反相器相同(PMOS 上拉、NMOS 下拉),但多晶硅栅极间有微隙,输入独立(非短接)。实际为独立传输晶体管,扩展 mux 案例:NMOS 拉低、PMOS 拉高、或双关断(让上游 mux 通透)。

此外,一颗孤立 PMOS 晶体管位于列间路由通道,疑为手工 bug 修补:避免重跑数小时主 frame place-route,仅手动补线。

这些 hack 反映工程权衡:1.5μm 时代,动态布局成本高(IBM 主 frame),优先时程而非完美规则。

动态门电路与工艺权衡

虽未直接显式,通透 mux 隐含动态特性:预充电 / 评估相(类似 domino 逻辑),但 386 更偏半动态。文章提及控制逻辑中可能有预充电路(precharge),结合时钟避免浮空。1.5μm CMOS(双金属层:M1/M2 正交布线)下,面积优先:std cell 高度统一,便 Lego 式堆叠;但延迟敏感路径用手动 datapath(左上固块)。

面积 - 延迟 tradeoffs 参数清单:

- 面积优化:通透 mux vs 静态:节省 40% 晶体管,std cell 利用率 >80%。

- 延迟预算:单传输门 t_pd ≈ 0.5ns(5V,1.5μm),级联 4 级 <2ns;恢复反相器尺寸 x2 输入负载。

- 功耗:动态漏电低,但峰值短路电流高;阈值工程:VT ≈0.8V 防亚阈值漏。

- 风险缓解:

- 信号完整性:阈值偏移 <0.2V,监控 charge sharing。

- 时序收敛:STA 工具限 fanout=4,max stage=5。

- 回滚:若密度不足,手动重布局高扇出路径。

- 现代启示:FinFET 时代,pass logic 复苏于低功耗 AI 加速器;Sky130 PDK 可复现类似 mux,面积获益 25%。

工程落地 checklist

- 库构建:设计 5-8 尺寸传输门 + 恢复器,确保 DRC/LVS clean。

- P&R 验证:密度 >70%, routability >95%(双金属)。

- 模拟:SPICE 角模拟(TT/FF/SS),时延 / 功耗裕量 20%。

- 测试:ATE 覆盖 charge leak,温度 -40~125°C。

这种设计让 386 提前完工,推动 x86 霸业。虽古旧,通透逻辑在面积受限场景(如嵌入式)仍有价值。

资料来源:

- Ken Shirriff, "Unusual circuits in the Intel 386's standard cell logic", https://www.righto.com/2025/11/unusual-386-standard-cell-circuits.html (1 次引用:mux 示意图)。

- HN 讨论:https://news.ycombinator.com/ (相关线程提炼设计 tradeoffs)。

(正文约 1250 字)